时间 :2023-03-02 浏览量:

深圳市美裕芯科技有限公司【分销TI处理器】供应AM6546BACDXA 具有千兆位 PRU-ICSS 的四核 Arm® Cortex®-A53 和双核 Arm Cortex-R5F Sitara™ 处理器 质量保证 !!!

AM6546BACDXA产品描述:

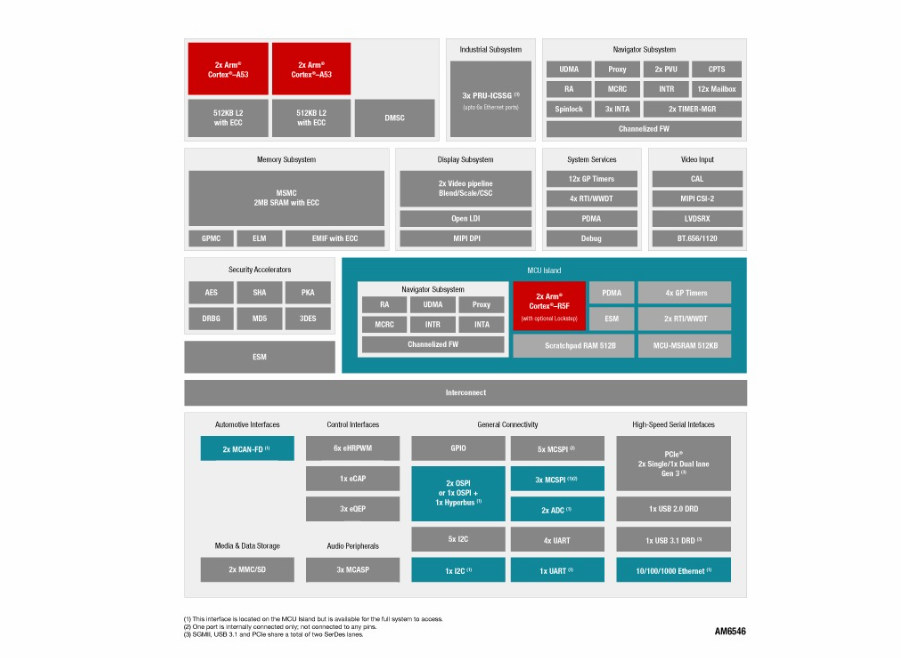

AM6546BACDXA 器件将四个或两个 Arm Cortex-A53 内核与双 Arm Cortex-R5F MCU 子系统(包括旨在帮助客户实现其最终产品功能安全目标的特性)和三个千兆位工业通信子系统 (PRU_ICSSG) 组合在一起,从而为功能安全应用实现支持 SoC 且具有工业连接和处理能力的高性能工业控制。 AM65xx 目前正在按照 IEC 61508 标准要求,接受 TÜV SÜD 的认证评估。

AM6546BACDXA 中的四个 Arm Cortex-A53 内核分布在两个具有共享 L2 存储器的双核集群中,以创建两个处理通道。 AM652x 中的两个 Arm Cortex-A53 内核可通过单个双核集群和两个单核集群选项提供。片上存储器、外设和互联中包含广泛的 ECC,可确保可靠性。整个 SoC 中包括旨在帮助客户设计可实现他们的功能安全目标的特性(正在等待 TÜV SÜD 评估结果)。除了 DMSC 管理的粒度防火墙之外,某些 AM654x 和 AM652x 器件上还提供了加密加速和安全启动功能。

AM6546BACDXA Arm Cortex-A53 RISC CPU 及 Arm Neon™ 扩展可实现可编程性,而双 Arm Cortex-R5F MCU 子系统可作为两个内核用于一般用途或用于锁步模式,以帮助满足功能安全应用的需求。PRU_ICSSG 子系统可用于提供最多六个工业以太网端口,如 Profinet IRT、TSN、Ethernet/IP 或 EtherCAT 等,或者用于标准千兆位以太网连接。

AM6546BACDXA产品特点:

存储器子系统:

• 高达 2MB 的片上 L3 RAM(具有 SECDED)

• 多核共享存储器控制器 (MSMC)

– 高达 2MB(2 组 × 1MB)的 SRAM(具有SECDED)

• 共享相干 2 级或 3 级存储器映射 SRAM

• 共享相干 3 级缓存

– 256 位处理器端口总线和 40 位物理地址总线

– 用于连接处理器或设备主机的相干统一双向接口

– L2、L3 缓存预热和后清除

– 具有饥饿限制的带宽管理

– 一个基础设置主接口

– 单个外部存储器主接口

– 支持分布式虚拟系统

– 支持内部 DMA 引擎 - 数据路由单元 (DRU)

– ECC 错误保护

• DDR 子系统 (DDRSS)

– 支持高达 DDR-1600 的 DDR4 存储器类型

– 32 位数据总线和 7 位 SECDED 总线

– 8 GB 全部可寻址空间

• 通用存储器控制器 (GPMC)

SafeTI™ 半导体组件:

• 专为功能安全应用而设计

• 根据 IEC 61508 标准的要求开发

• 达到 SIL-3 的系统完整性

• 对于 MCU 安全岛,包含足够的诊断以达到 SIL-2的随机故障完整性要求

• 对于 SoC 的其余部分,包含足够的诊断以达到SIL-2 的随机故障完整性要求

• 此外,还需要配置足够的架构指标,以实现考虑特定安全概念的 SIL-3 的执行(如软件互惠式比较)

• 提供功能安全手册

• 安全相关认证

– TÜV SÜD 组件级功能安全认证 [正在认证]

• 功能安全特性:

– 计算临界存储器的 ECC 或奇偶校验和内部总线互联

– 有助于防止干扰 (FFI) 的防火墙

• 适用于 CPU、高端计时器和片上 RAM 的内置自检 (BIST)

– 针对诊断测试的硬件错误注入支持

– 用于捕获功能安全相关错误的错误信号模块(ESM)

– 电压、温度和时钟监控

– 多个时钟域内的窗口式和非窗口式看门狗计时器

• MCU 岛

– 隔离了双核 Arm® Cortex®-R5F 微处理器子系统,

– 独立的电压、时钟、复位和专用外设

– 与 SoC 其余部分的内部 MCSPI 连接

版权所有 2022 深圳市美裕芯科技有限公司 电话:+86-13530718420 粤ICP备2022094269号-1